반도체, 5나노미터 설계기술 개발

|

KAIST 김상욱 교수팀, 초미세 패턴 활용 … 집적도‧용량 확대 기대 화학뉴스 2014.05.02

국내 연구진이 반도체 설계의 집적도를 획기적으로 늘려주는 신기술을 개발했다.

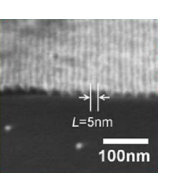

반도체 공정의 한계로 거론돼 온 10나노미터 공정의 벽을 깰 수 있는 계기가 될 것으로 기대되고 있다. 김상욱 KAIST 교수팀과 권세훈 부산대 교수팀은 5나노미터급 초미세회로를 제작할 수 있는 기술을 개발했다. 반도체를 설계할 때 회로 폭이 10나노미터보다 줄어들면 회로 사이가 너무 가까워 전류를 제어하기 어려운 문제가 있었다.  특히, 감광재료와 레이저광을 이용하는 광 리소그래피(Optical Lithography) 공정도 초미세회로에 적용하기 어려워 10나노미터는 반도체 공정의 한계로 여겨졌다. 연구팀은 광 리소그래피 공정 대신 고분자 물질들이 스스로 조립되는 분자자기조립 현상과 원자를 층층이 쌓는 원자층 증착법을 융합했다. 산화알루미늄을 5나노미터 두께로 쌓고 불필요한 부분을 제거해 5나노미터 간격의 초미세 패턴을 만들었으며 마스크 형틀을 이용해 기판 위에 똑같은 패턴을 만드는 데 성공했다. 연구팀 김상국 교수는 “개발된 기술을 활용하면 현재까지 불가능으로 여겨졌던 10나노미터 이하의 반도체 공정 설계가 가능해질 것”이라며 “집적도가 높아지면서 반도체 용량도 획기적으로 늘릴 수 있는 기술적 토대를 마련했다”고 강조했다. |

한줄의견

관련뉴스

| 제목 | 날짜 | 첨부 | 스크랩 |

|---|---|---|---|

| [반도체소재] 반도체, 테이프‧필름 1.5배 “급성장” | 2026-02-27 | ||

| [화학경영] 화학기업, 반도체 소재가 살길이다! | 2026-02-25 | ||

| [반도체소재] 코스모신소재, 반도체 슈퍼사이클 올라탄다! | 2026-02-23 |

| 제목 | 날짜 | 첨부 | 스크랩 |

|---|---|---|---|

| [폴리머] PC·PS 대체 본격화 반도체·EV 적용 기대한다! | 2026-02-27 | ||

| [기술/특허] 머크, 반도체 박막소재 프로세스 AI로 전환 | 2026-02-20 |