국내 연구진이 그래핀(Graphene)을 여러층 쌓아 반도체 회로의 집적도를 높일 수 있는 기술을 개발했다.

이영희 기초과학연구원(IBS) 나노구조물리연구단장 연구팀은 4층짜리 다층 그래핀을 넓고 고르게 합성하는 방법을 세계 최초로 개발했다고 7월28일 밝혔다.

연구 성과는 네이처 자매지인 네이처 나노테크놀로지(Nature Nanotechnology) 7월28일자로 게재됐다.

연구 성과는 네이처 자매지인 네이처 나노테크놀로지(Nature Nanotechnology) 7월28일자로 게재됐다.

그래핀은 탄소 원자가 육각형으로 평평하게 배열된 2차원 물질로 전기가 잘 통하고 투명·유연해 반도체 소재로 사용되고 있다.

그래핀을 여러층으로 쌓은 다층 그래핀을 활용하면 반도체 회로를 더 작게 만들 수 있는 것으로 알려졌다.

다만, 그래핀을 만들기 위해 고온 환경에서 메탄(Methane) 기체를 탄소와 수소로 분해한 후 탄소만 구리 기판에 달라붙게 하는 화상기상증착법(CVD)을 사용하고 있는 가운데 그래핀을 여러층으로 쌓기 위해 구리 대신 니켈을 기판으로 활용하면 층수가 불균일해 성능 구현에 한계가 있다는 단점이 있다.

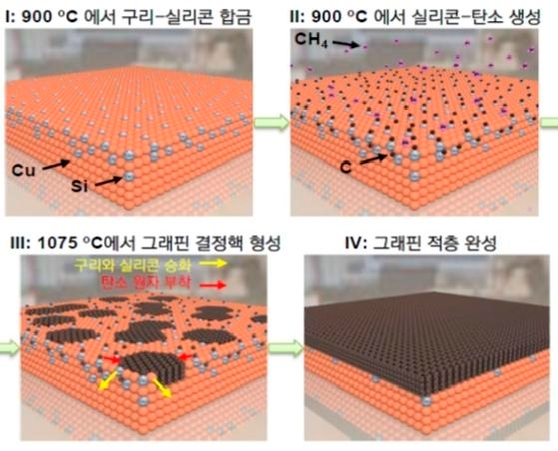

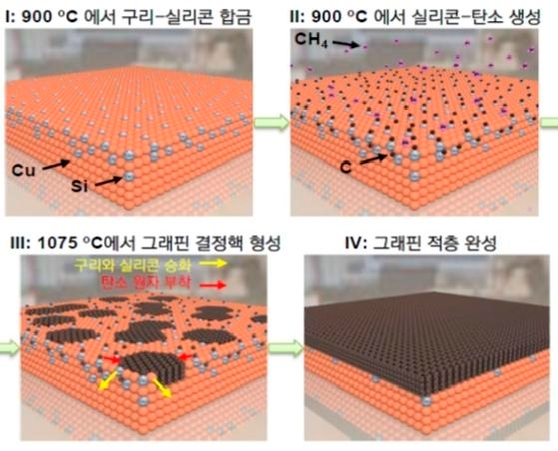

이에 연구팀은 섭씨 900도 고온에서 구리 기판에 실리콘(Silicone)을 증착시켜 구리-실리콘 합금을 만들었고 해당 합금을 기판으로 사용해 구리만 사용했을 때보다 탄소가 더 고르게 증착된다는 사실을 발견했다.

연구팀은 새로 개발한 기술로 4층짜리 다층 그래핀을 가로·세로 수센티미터 크기로 고르게 만드는데 성공했다. 메탄의 농도를 조절해 층수도 결정할 수 있는 것으로 알려졌다.

연구팀은 “층수에 비례해 전기저항이 작아지고 전기가 잘 통하게 된다”며 “다양한 반도체소자 기술에 응용할 수 있는 특성”이라고 강조했다.

연구팀은 앞으로 대량 합성실험을 반복해 품질 안정성을 높이는 연구를 수행하고 다층 그래핀을 다양한 전자기기에 적용해 성능 차이를 확인할 방침이다. (K)

연구 성과는 네이처 자매지인 네이처 나노테크놀로지(Nature Nanotechnology) 7월28일자로 게재됐다.

연구 성과는 네이처 자매지인 네이처 나노테크놀로지(Nature Nanotechnology) 7월28일자로 게재됐다.